## Lecture 3 : Gate-Level Minimization

#### Outline

four-variable Karnaugh Map

NAND and NOR Implementations

Other Two-Level Implementations

Exclusive-OR Function

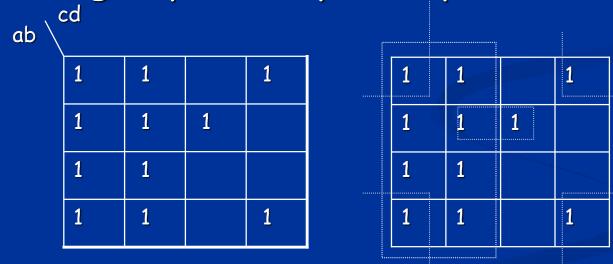

#### Four-Variable Maps YΖ 00 01 10 11 WX mo $m_1$ 00 m<sub>3</sub> $m_2$ ΧZ $m_6$ 01 $m_4$ $m_7$ $m_5$ m<sub>12</sub> $m_{15}$ 11 $m_{14}$ $m_{13}$ $m_{11}$ 10 $m_8$ $m_9$ $m_{10}$

- Top cells are adjacent to bottom cells. Leftedge cells are adjacent to right-edge cells.

- Note variable ordering (WXYZ).

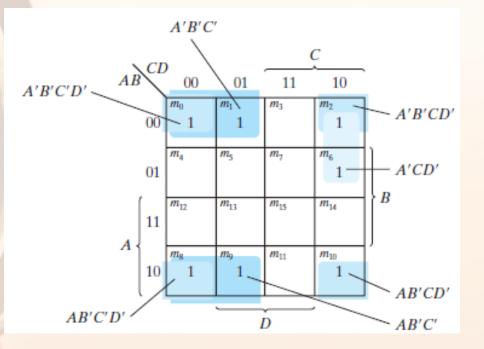

Simplify the following Boolean function  $(A,B,C,D) = \sum m(0,1,2,4,5,7,8,9,10,12,13).$

First put the function g() into the map, and then group as many 1s as possible.

q(A,B,C,D) = c'+b'd'+a'bd

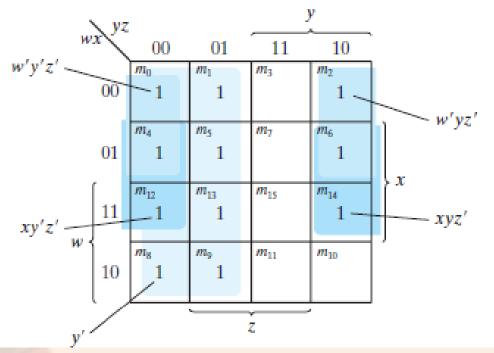

#### **EXAMPLE 3.5** Simplify the Boolean function $F(w, x, y, z) = \Sigma(0, 1, 2, 4, 5, 6, 8, 9, 12, 13, 14)$

F = y' + w'z' + xz'

#### **EXAMPLE 3.6** Simplify the Boolean function

F = A'B'C' + B'CD' + A'BCD' + AB'C'

F = B'D' + B'C' + A'CD'

# Example

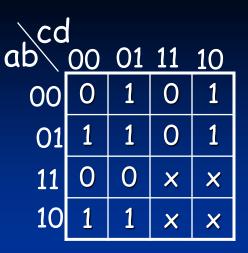

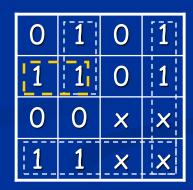

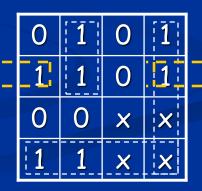

- Simplify the function f(a,b,c,d) whose K-map is shown at the right.

- f = a'c'd+ab'+cd'+a'bc'

or

- f = a'c'd+ab'+cd'+a'bd'

- The middle two terms are EPIs, while the first and last terms are selected to

cover the minterms  $m_1$ ,  $m_4$ , and  $m_5$ .

(There's a third solution!)

#### **EXAMPLE 3.7**

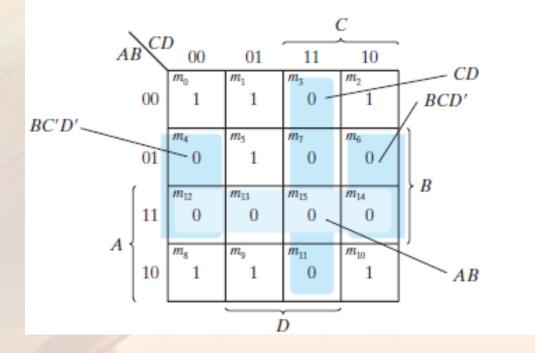

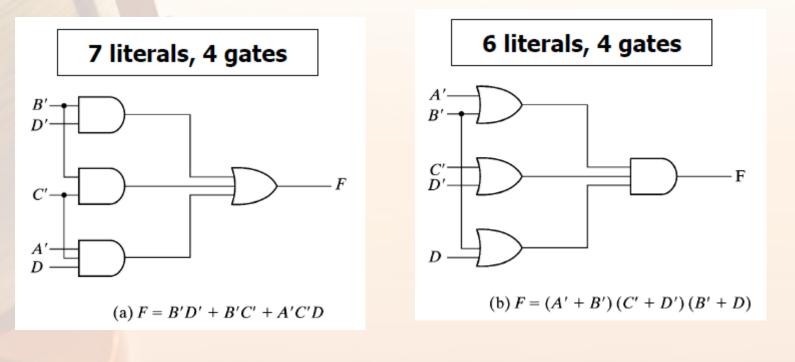

Simplify the following Boolean function into (a) sum-ofproducts form and (b) product-of-sums form:  $F(A, B, C, D) = \Sigma(0, 1, 2, 5, 8, 9, 10)$

(b) F = (A' + B')(C' + D')(B' + D)

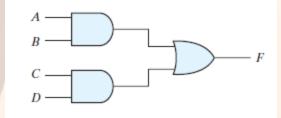

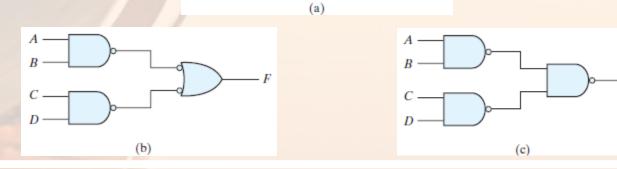

#### **Two Gate Implementations**

Sometimes product-of-sums representations may have smaller implementations

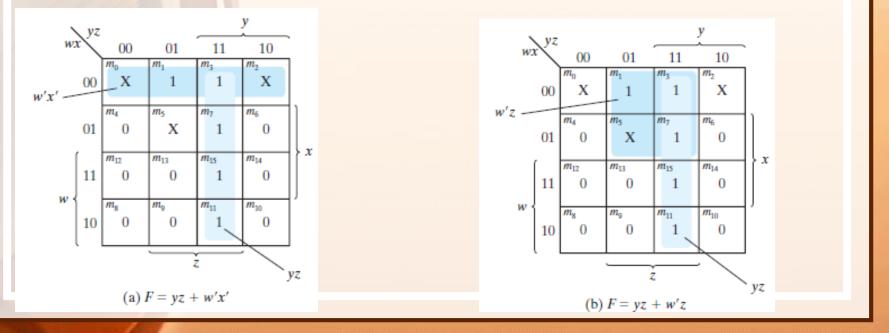

#### **Don't Care Conditions**

- $\Box X = don't$  care (can be 0 or 1)

- Don't cares can be included to form a larger cube, but not necessary to be completely covered

$\Box \text{ Ex: } F(w, x, y, z) = \Sigma(1, 3, 7, 11, 15) \ d(w, x, y, z) = \Sigma(0, 2, 5)$

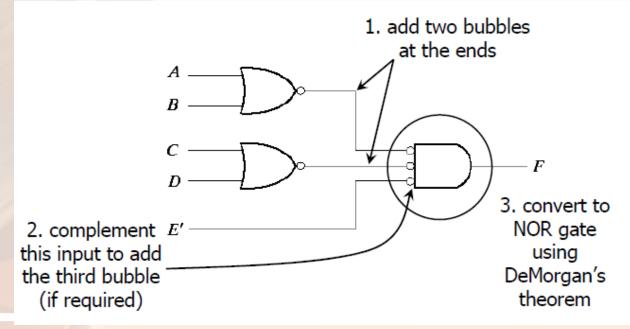

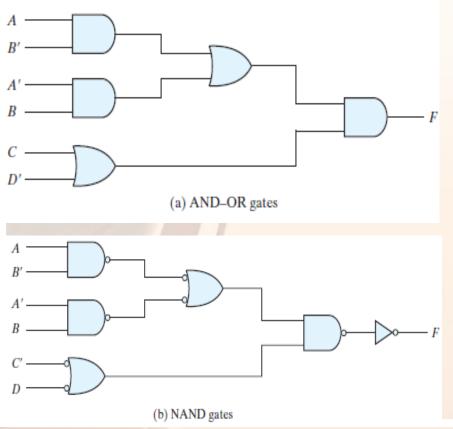

#### **NAND** and NOR Implementation

Digital circuits are frequently constructed with NAND or NOR gates rather than with AND and OR gate

□ NAND and NOR gates are much easier to fabricate

□ NAND or NOR gates are both universal gates

Any digital system can be implemented with only NAND gates or NOR gates

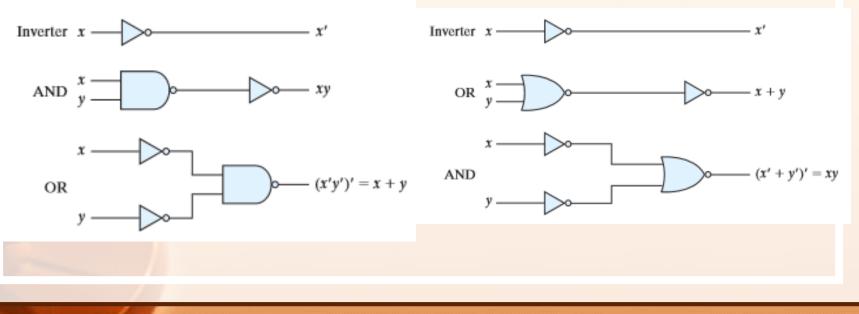

#### **Alternative Graphic Symbols**

To facilitate the conversion to NAND or NOR logic, it is convenient to define alternative graphic symbols

"Bubble" means complement

#### **Two-Level Implementation (NAND)**

It's easy to implement a Boolean function with only NAND gates if converted from a sum of products form

$\Box \text{ Ex: } F = AB + CD = ((AB)'(CD)')'$

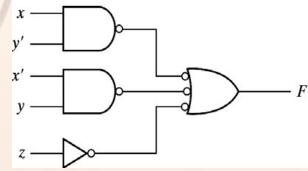

#### **EXAMPLE 3.9**

Implement the following Boolean function with NAND gates:  $F(x, y, z) = \Sigma(1, 2, 3, 4, 5, 7)$

Procedures:

- 1. Simplify the function in sum of products

- 2. Draw NAND gates for the first level

- 3. Draw a single AND-invert or invert-OR in the second level

- 4. Add an inverter at the first level for the term with a single literal

#### **Two-Level Implementation (NOR)**

It's easy to implement a Boolean function with only NOR gates if converted from a product of sums form

$\Box Ex: F = (A+B)(C+D)E$

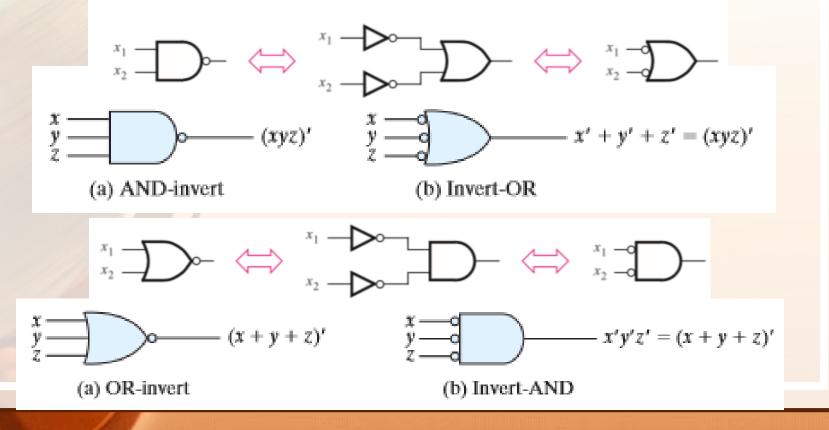

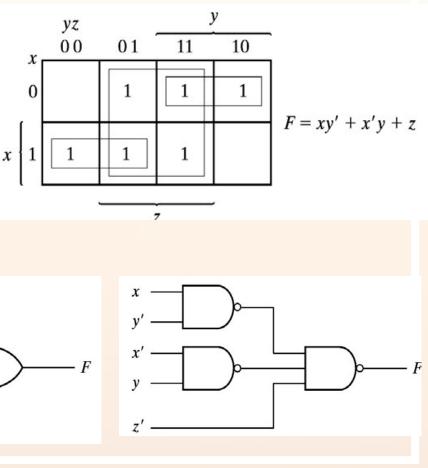

#### **Multilevel NAND Circuits**

Implementing F = (AB' + A'B) (C + D')

#### □ Procedures:

- 1. Convert all AND gates to NAND gates with ANDinvert symbols

- 2. Convert all OR gates to NAND gates with invert-OR symbols

- 3. Check all bubbles and insert an inverter for the bubble that are not compensated by another bubble

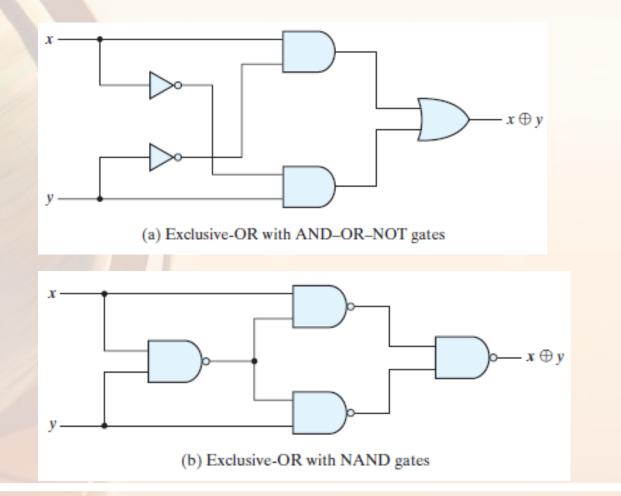

### **Exclusive-OR (XOR) Function**

- $\square$  XOR is often denoted by the symbol  $\oplus$

- Logic operation of XOR

- $\Box X \oplus Y = XY' + X'Y$

- Equal to 1 if only x is equal to 1 or if only y is equal to 1, but not when both are equal to 1

- □ It's complement, exclusive-NOR (XNOR), is often denoted by the symbol ⊙

- Logic operation

- $\Box X \odot Y = XY + X'Y'$

- It is equal to 1 if both x and y are equal to 1 or if both are equal to 0

- Seldom used in general Boolean functions

- Particularly useful in arithmetic operations and error detection and correction circuits

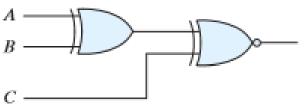

#### **Exclusive-OR Implementations**

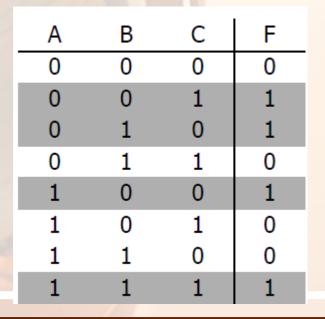

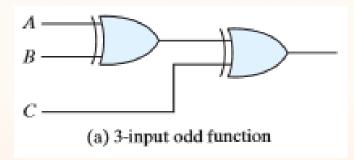

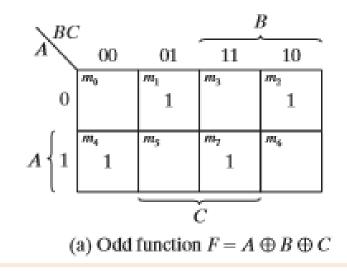

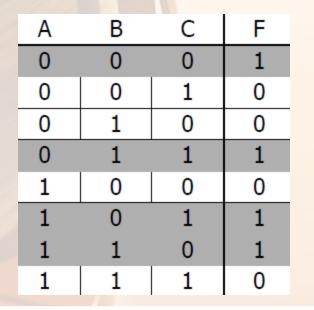

### **Odd Function**

The multiple-variable XOR operation is defined as an odd function

TRUE when no. of "1" in inputs is odd

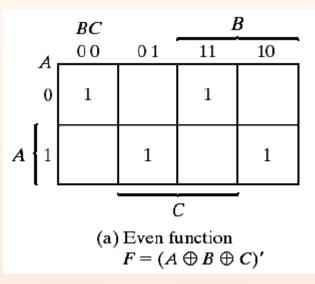

#### **Even Function**

The multiple-variable XNOR operation is defined as an even function

TRUE when no. of "1" in inputs is even

(b) 3-input even function

#### **Parity Generation and Checking**

- An extra parity bit is often added and checked at the receiving end for error

- The circuit that generates the parity bit in the transmitter is called a parity generator

- The circuit that checks the parity in the receiver is called a parity checker

- Exclusive-OR functions are very useful to construct such circuits

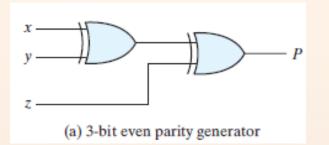

#### **Parity Generator**

- **For even** parity:

- The total number of "1" (including P) is even

- The number of "1" at inputs is odd

- Generated with an XOR gate (odd function)

- $\square P = x \oplus y \oplus z \text{ (for 3-bit message)}$

- Similarly, odd parity can be generated with an XNOR gate

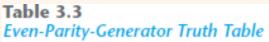

| Three-Bit Message |   |   | Parity Bit |

|-------------------|---|---|------------|

| x                 | y | z | Р          |

| 0                 | 0 | 0 | 0          |

| 0                 | 0 | 1 | 1          |

| 0                 | 1 | 0 | 1          |

| 0                 | 1 | 1 | 0          |

| 1                 | 0 | 0 | 1          |

| 1                 | 0 | 1 | 0          |

| 1                 | 1 | 0 | 0          |

| 1                 | 1 | 1 | 1          |

$P = x \bigoplus y \bigoplus z$

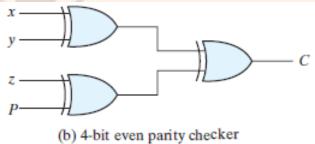

### **Parity Checker**

Table 3.4Even-Parity-Checker Truth Table

| For even parity, the total<br>number of "1" in the message<br>is even |

|-----------------------------------------------------------------------|

| An error occurs when the received number of "1" is odd                |

| An XOR gate (odd function)                                            |

| can detect such an error                                              |

| Has n+1 inputs                                                        |

| Four Bits<br>Received |   |   |   | Parity Error<br>Check |

|-----------------------|---|---|---|-----------------------|

| x                     | y | z | Р | с                     |

| 0                     | 0 | 0 | 0 | 0                     |

| 0                     | 0 | 0 | 1 | 1                     |

| 0                     | 0 | 1 | 0 | 1                     |

| 0                     | 0 | 1 | 1 | 0                     |

| 0                     | 1 | 0 | 0 | 1                     |

| 0                     | 1 | 0 | 1 | 0                     |

| 0                     | 1 | 1 | 0 | 0                     |

| 0                     | 1 | 1 | 1 | 1                     |

| 1                     | 0 | 0 | 0 | 1                     |

| 1                     | 0 | 0 | 1 | 0                     |

| 1                     | 0 | 1 | 0 | 0                     |

| 1                     | 0 | 1 | 1 | 1                     |

| 1                     | 1 | 0 | 0 | 0                     |

| 1                     | 1 | 0 | 1 | 1                     |

| 1                     | 1 | 1 | 0 | 1                     |

| 1                     | 1 | 1 | 1 | 0                     |

$C = x \oplus y \oplus z \oplus P$